set_disable_timing

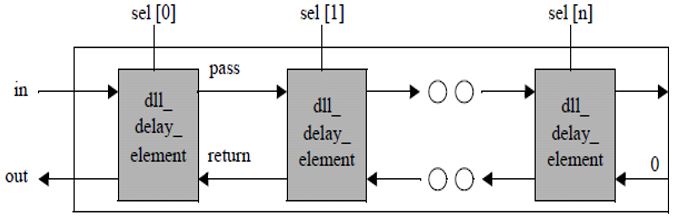

Sometimes, it is necessary to add constraint, such as set_disable_timing to let tool ignore timing path which should not be checked, critical path would be fixed by tool correctly.

set_disable_timing -from in1 -to pass [get_cells dll/dll_delay_line_master/delay_0] set_disable_timing -from in1 -to pass [get_cells dll/dll_delay_line_clk_wr/delay_0] #ezp set_disable_timing -from in1 -to pass [get_cells dll_delay_line/delay_0] #ezp set_disable_timing -from in1 -to pass [get_cells dll/dll_delay_line_wr_dqs/delay_0] set_disable_timing -from in1 -to pass [get_cells dll/dll_delay_line_rd_dqs/delay_0]

set_disable_timing -from ret -to out1 [get_cells dll/dll_delay_line_master/delay_0] set_disable_timing -from ret -to out1 [get_cells dll/dll_delay_line_clk_wr/delay_0] #ezp set_disable_timing -from ret -to out1 [get_cells dll_delay_line/delay_0] #ezp set_disable_timing -from ret -to out1 [get_cells dll/dll_delay_line_wr_dqs/delay_0] set_disable_timing -from ret -to out1 [get_cells dll/dll_delay_line_rd_dqs/delay_0]

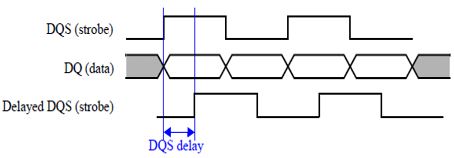

For example, delay_element is only used for DDR DQS signal delay which is not timing path. Data transfer successfully only when the data strobe signal falls with the data eye with sufficient setup and hold margin, Data-Valid-Window shrink along with the upgrade from DDR1 to DDR4 (seup/hold margin shrink with period shrink)

Two key points: 1. Good data skew to achieve maximizing the open eye. 2. Accurate shift the DQS to the date bus center and jitter control to maximize the setup/hold margin.

one delay_line is combined by 128 delay_elements,

so

set_disable_timing -from delay_line_begin_element_input_1 -to delay_line_begin_element_pass

set_disable_timing -from delay_line_begin_element_return -to delay_line_begin_element_out_1

Comments

So empty here ... leave a comment!