Clock Tree Synthesis

In clock tree synthesis, do ONE thing only, insert CLK INV (NOT CKBUFF !) which could fix rising and falling transition/duty, to min clock tree latency and skew, balance sink/leaf pins which should be balanced, don’t balance pins which should not be balanced.

CTS Macro Model

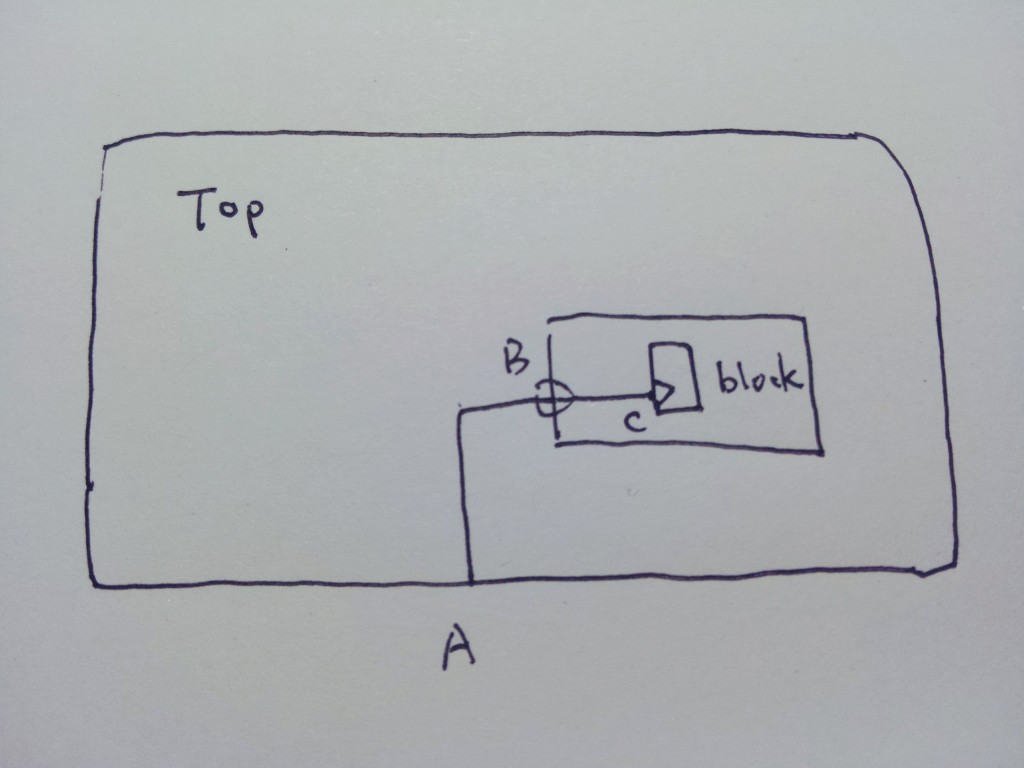

Let tool know the segment of clock path latency which from assertion pin to sink/leaf pin, balance sink/leaf pins considering this segment. For example, one clock from chip/top level to block level in hierarchy, clock path from the junction point of PHY_TOP and data_slice to reg/ck pin in data_slice.

In the picture below, clock root pin is A, the segment of clock path latency from point B to point C is CTS Macro Model delay.

The value of Macro Model in CTS spec file below is 550ps.

In PHY_TOP CTS spec file: MacroModel pin databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy 550ps 550ps 550ps 550ps 0fF

Tell tool that the latency from port of data_slice (block level) to reg/ck in data_slice is about 550ps. The report below is part of PHY_TOP STA. Full STA timing report: STA_report_PHY_TOP

Path 2: MET Setup Check with Pin databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/wr_l_reg/CKN

Endpoint: databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/wr_l_reg/D (v) checked with trailing edge of ‘clk_dqs_0_phase_0’

Beginpoint: databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/write_data_l_reg_reg/Q (v) triggered by leading edge of ‘clk_phase_0’

Path Groups: {reg2reg}

Other End Arrival Time 2.068

– Setup 0.075

+ Phase Shift 0.000

+ CPPR Adjustment 0.097

– Uncertainty 0.105

= Required Time 1.985

– Arrival Time 1.980

= Slack Time 0.005

Clock Fall Edge 1.250

= Beginpoint Arrival Time 1.250

Timing Path:

————————————————————————————————————————————————————–

Pin Arc Cell Delay Arrival Incr Slew Load Fanout User Generated Clock

Time Delay Derate Adjustment

————————————————————————————————————————————————————–

clk_ctlr_sync clk_ctlr_sync v 1.250 0.200 0.003 1

clk_ctlr_sync_I_xIOx/I CLKBUFV8_12TR35 0.000 1.250 0.000 0.200 0.003 1 1.000

clk_ctlr_sync_I_xIOx/Z I v -> Z v CLKBUFV8_12TR35 0.125 1.375 0.000 0.047 0.019 1.000

clk_ctlr_sync_N_xIOx__L1_I0/I CLKINV12_12TR35 0.004 1.379 0.000 0.047 0.019 1 1.000

clk_ctlr_sync_N_xIOx__L1_I0/ZN I v -> ZN ^ CLKINV12_12TR35 0.037 1.416 0.000 0.024 0.019 1.000

clk_ctlr_sync_N_xIOx__L2_I0/I CLKINV12_12TR35 0.004 1.420 0.000 0.025 0.019 1 1.000

clk_ctlr_sync_N_xIOx__L2_I0/ZN I ^ -> ZN v CLKINV12_12TR35 0.027 1.447 0.000 0.029 0.017 1.000

clk_ctlr_sync_N_xIOx__L3_I0/I CLKINV12_12TR35 0.003 1.450 0.000 0.030 0.017 1 1.000

clk_ctlr_sync_N_xIOx__L3_I0/ZN I v -> ZN ^ CLKINV12_12TR35 0.021 1.471 0.000 0.010 0.005 1.000

clk_ctlr_sync_N_xIOx__I29/I CLKINV16_12TR35 0.000 1.471 0.000 0.010 0.005 1 1.000

clk_ctlr_sync_N_xIOx__I29/ZN I ^ -> ZN v CLKINV16_12TR35 0.010 1.481 0.000 0.009 0.005 1.000

clk_ctlr_sync_N_xIOx__I30/I CLKINV16_12TR35 0.000 1.482 0.000 0.009 0.005 1 1.000

clk_ctlr_sync_N_xIOx__I30/ZN I v -> ZN ^ CLKINV16_12TR35 0.013 1.494 0.000 0.019 0.026 1.000

clk_ctlr_sync_N_xIOx__L4_I0/I CLKINV12_12TR35 0.008 1.502 0.000 0.023 0.026 1 1.000

clk_ctlr_sync_N_xIOx__L4_I0/ZN I ^ -> ZN v CLKINV12_12TR35 0.022 1.525 0.000 0.016 0.008 1.000

databahn_dll_phy/clk_ctlr_sync clk_ctlr_sync v databahn_dll_phy 1.525 1.000 clk_ctlr_phase_0 Adj. = 0.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I0/I

CLKINV12_12TR35 0.001 1.525 0.000 0.016 0.008 1 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I0/ZN

I v -> ZN ^ CLKINV12_12TR35 0.016 1.541 0.000 0.010 0.009 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I1/I

CLKINV16_12TR35 0.001 1.542 0.000 0.010 0.009 1 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I1/ZN

I ^ -> ZN v CLKINV16_12TR35 0.011 1.553 0.000 0.008 0.004 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I27/I

CLKINV12_12TR35 0.000 1.553 0.000 0.008 0.004 1 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I27/ZN

I v -> ZN ^ CLKINV12_12TR35 0.009 1.562 0.000 0.006 0.004 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I28/I

CLKINV12_12TR35 0.000 1.562 0.000 0.006 0.004 1 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I28/ZN

I ^ -> ZN v CLKINV12_12TR35 0.018 1.580 0.000 0.023 0.014 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L1_I0/I

CLKINV16_12TR35 0.001 1.581 0.000 0.023 0.014 2 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L1_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.022 1.603 0.000 0.020 0.026 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L2_I0/I

CLKINV16_12TR35 0.006 1.609 0.000 0.022 0.026 1 1.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L2_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.028 1.637 0.000 0.032 0.026 1.000

databahn_dll_phy/dll_phy_pll_clk_source/deskew_pll/FREF

PLLSM28HKLVDESKEW 0.004 1.641 0.000 0.016 0.026 2 1.000

databahn_dll_phy/dll_phy_pll_clk_source/deskew_pll/FOUTP

FREF v -> FOUTP ^ PLLSM28HKLVDESKEW 0.000 0.391 0.000 0.017 0.026 1.000 clk_phase_0 Adj. = -1.250

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_pll_clkgate/hic_dnt_pll_clkgate/CK

CLKLANQV12_12TR35 0.001 0.392 0.000 0.034 0.026 2 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_pll_clkgate/hic_dnt_pll_clkgate/Q

CK ^ -> Q ^ CLKLANQV12_12TR35 0.052 0.445 0.000 0.012 0.004 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand0/A1

CLKNAND2V8_12TR35 0.000 0.445 0.000 0.012 0.004 1 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand0/ZN

A1 ^ -> ZN v CLKNAND2V8_12TR35 0.015 0.460 0.000 0.014 0.004 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand2/A1

CLKNAND2V8_12TR35 0.000 0.460 0.000 0.014 0.004 1 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand2/ZN

A1 v -> ZN ^ CLKNAND2V8_12TR35 0.014 0.474 0.000 0.009 0.004 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_phybyp_clkgate/hic_dnt_pll_clkgate/CK

CLKLANQV12_12TR35 0.000 0.474 0.000 0.009 0.004 1 1.000

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_phybyp_clkgate/hic_dnt_pll_clkgate/Q

CK ^ -> Q ^ CLKLANQV12_12TR35 0.042 0.516 0.000 0.031 0.026 1.000

databahn_dll_phy/dll_phy_lp_control/inst_hic_lp_clkgate_phy/hic_dnt_io_clkgate/CK

CLKLANQV12_12TR35 0.001 0.517 0.000 0.031 0.026 2 1.000

databahn_dll_phy/dll_phy_lp_control/inst_hic_lp_clkgate_phy/hic_dnt_io_clkgate/Q

CK ^ -> Q ^ CLKLANQV12_12TR35 0.048 0.565 0.000 0.025 0.019 1.000

databahn_dll_phy/lp_clk_phy__L1_I0/I

CLKINV16_12TR35 0.003 0.567 0.000 0.025 0.019 2 1.000

databahn_dll_phy/lp_clk_phy__L1_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.028 0.595 0.000 0.042 0.035 1.000

databahn_dll_phy/lp_clk_phy__L2_I0/I

CLKINV16_12TR35 0.015 0.610 0.000 0.048 0.035 1 1.000

databahn_dll_phy/lp_clk_phy__L2_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.038 0.647 0.000 0.026 0.032 1.000

databahn_dll_phy/lp_clk_phy__L3_I0/I

CLKINV16_12TR35 0.011 0.658 0.000 0.032 0.032 1 1.000

databahn_dll_phy/lp_clk_phy__L3_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.034 0.692 0.000 0.044 0.036 1.000

databahn_dll_phy/lp_clk_phy__L4_I0/I

CLKINV16_12TR35 0.014 0.705 0.000 0.049 0.036 1 1.000

databahn_dll_phy/lp_clk_phy__L4_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.038 0.744 0.000 0.028 0.037 1.000

databahn_dll_phy/lp_clk_phy__L5_I0/I

CLKINV16_12TR35 0.013 0.757 0.000 0.037 0.037 1 1.000

databahn_dll_phy/lp_clk_phy__L5_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.036 0.793 0.000 0.042 0.034 1.000

databahn_dll_phy/lp_clk_phy__L6_I0/I

CLKINV16_12TR35 0.013 0.805 0.000 0.047 0.034 1 1.000

databahn_dll_phy/lp_clk_phy__L6_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.037 0.843 0.000 0.028 0.038 1.000

databahn_dll_phy/lp_clk_phy__L7_I0/I

CLKINV16_12TR35 0.013 0.856 0.000 0.037 0.038 1 1.000

databahn_dll_phy/lp_clk_phy__L7_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.034 0.890 0.000 0.032 0.024 1.000

databahn_dll_phy/lp_clk_phy__L8_I0/I

CLKINV16_12TR35 0.006 0.895 0.000 0.033 0.024 1 1.000

databahn_dll_phy/lp_clk_phy__L8_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.028 0.923 0.000 0.022 0.026 1.000

databahn_dll_phy/dll_phy_slice_core/FE_ECOC0_lp_clk_phy/I

CLKINV8_12TR35 0.006 0.929 0.000 0.024 0.026 2 1.000

databahn_dll_phy/dll_phy_slice_core/FE_ECOC0_lp_clk_phy/ZN

I ^ -> ZN v CLKINV8_12TR35 0.019 0.948 0.000 0.012 0.003 1.000

databahn_dll_phy/dll_phy_slice_core/FE_ECOC1_lp_clk_phy/I

CLKINV8_12TR35 0.000 0.948 0.000 0.012 0.003 1 1.000

databahn_dll_phy/dll_phy_slice_core/FE_ECOC1_lp_clk_phy/ZN

I v -> ZN ^ CLKINV8_12TR35 0.014 0.962 0.000 0.010 0.006 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L1_I0/I

CLKINV16_12TR35 0.000 0.963 0.000 0.010 0.006 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L1_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.011 0.973 0.000 0.008 0.004 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L2_I0/I

CLKINV12_12TR35 0.000 0.973 0.000 0.008 0.004 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L2_I0/ZN

I v -> ZN ^ CLKINV12_12TR35 0.009 0.983 0.000 0.005 0.003 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_I_xIOx/I

CLKBUFV8_12TR35 0.000 0.983 0.000 0.005 0.003 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_I_xIOx/Z

I ^ -> Z ^ CLKBUFV8_12TR35 0.031 1.014 0.000 0.017 0.009 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/data_slice_data_byte_disable/inst_hic_lp_clkgate_dfi_data_byte_disable_phy/hic_dnt_io_clkgate/CK

CLKLANQV2_12TR35 0.001 1.014 0.000 0.017 0.009 2 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/data_slice_data_byte_disable/inst_hic_lp_clkgate_dfi_data_byte_disable_phy/hic_dnt_io_clkgate/Q

CK ^ -> Q ^ CLKLANQV2_12TR35 0.072 1.087 0.002 0.063 0.009 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L1_I0/I

CLKINV12_12TR35 0.000 1.087 0.000 0.064 0.009 2 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L1_I0/ZN

I ^ -> ZN v CLKINV12_12TR35 0.051 1.137 0.000 0.035 0.017 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L2_I0/I

CLKINV16_12TR35 0.003 1.140 0.000 0.035 0.017 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L2_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.026 1.166 0.000 0.014 0.013 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L3_I0/I

CLKINV16_12TR35 0.001 1.167 0.000 0.014 0.013 3 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L3_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.012 1.179 0.000 0.009 0.005 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L4_I0/I

CLKINV12_12TR35 0.000 1.179 0.000 0.009 0.005 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L4_I0/ZN

I v -> ZN ^ CLKINV12_12TR35 0.010 1.189 0.000 0.007 0.005 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L5_I0/I

CLKINV16_12TR35 0.000 1.189 0.000 0.007 0.005 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L5_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.013 1.203 0.000 0.015 0.011 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L6_I0/I

CLKINV16_12TR35 0.001 1.204 0.000 0.015 0.011 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L6_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.017 1.221 0.000 0.015 0.019 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L7_I0/I

CLKINV12_12TR35 0.002 1.223 0.000 0.015 0.019 2 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L7_I0/ZN

I ^ -> ZN v CLKINV12_12TR35 0.022 1.245 0.000 0.026 0.015 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L8_I0/I

CLKINV16_12TR35 0.002 1.247 0.000 0.026 0.015 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L8_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.021 1.269 0.000 0.011 0.010 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L9_I0/I

CLKINV16_12TR35 0.001 1.270 0.000 0.011 0.010 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L9_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.016 1.286 0.000 0.017 0.013 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L10_I0/I

CLKINV16_12TR35 0.001 1.287 0.000 0.017 0.013 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L10_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.020 1.307 0.000 0.019 0.026 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__I12/I

CLKINV12_12TR35 0.003 1.310 0.000 0.019 0.026 4 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__I12/ZN

I ^ -> ZN v CLKINV12_12TR35 0.017 1.327 0.000 0.011 0.004 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__I11/I

CLKINV12_12TR35 0.000 1.327 0.000 0.011 0.004 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__I11/ZN

I v -> ZN ^ CLKINV12_12TR35 0.011 1.338 0.000 0.007 0.004 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L11_I2/I

CLKINV12_12TR35 0.000 1.338 0.000 0.007 0.004 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L11_I2/ZN

I ^ -> ZN v CLKINV12_12TR35 0.019 1.357 0.000 0.030 0.018 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L12_I2/I

CLKINV12_12TR35 0.003 1.360 0.000 0.030 0.018 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L12_I2/ZN

I v -> ZN ^ CLKINV12_12TR35 0.029 1.389 0.000 0.019 0.020 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L13_I3/I

CLKINV16_12TR35 0.001 1.389 0.000 0.019 0.020 4 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L13_I3/ZN

I ^ -> ZN v CLKINV16_12TR35 0.025 1.414 0.001 0.029 0.023 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L14_I4/I

CLKINV16_12TR35 0.005 1.419 0.000 0.030 0.023 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L14_I4/ZN

I v -> ZN ^ CLKINV16_12TR35 0.028 1.447 0.000 0.018 0.021 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L15_I6/I

CLKINV12_12TR35 0.002 1.449 0.000 0.019 0.021 2 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L15_I6/ZN

I ^ -> ZN v CLKINV12_12TR35 0.031 1.480 0.000 0.039 0.027 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L16_I20/I

CLKINV16_12TR35 0.001 1.481 0.000 0.039 0.027 4 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L16_I20/ZN

I v -> ZN ^ CLKINV16_12TR35 0.039 1.520 0.000 0.022 0.027 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/write_data_l_reg_reg/CK

SDRNQV2_12TR35 0.002 1.521 0.000 0.022 0.027 18 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/write_data_l_reg_reg/Q

CK ^ -> Q v SDRNQV2_12TR35 0.137 1.658 0.000 0.014 0.001 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_PHC1026_n_9740/I

BUFV5RQ_12TR35 0.000 1.658 0.000 0.014 0.001 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_PHC1026_n_9740/Z

I v -> Z v BUFV5RQ_12TR35 0.046 1.704 0.000 0.022 0.009 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/g321/I1

MUX2CV2_12TR35 0.004 1.708 0.004 0.022 0.009 3 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/g321/Z

I1 v -> Z v MUX2CV2_12TR35 0.055 1.763 0.000 0.034 0.003 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_RC_206_0/I

INV2_12TR35 0.004 1.767 0.003 0.034 0.003 2 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_RC_206_0/ZN

I v -> ZN ^ INV2_12TR35 0.032 1.799 0.000 0.018 0.002 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_RC_225_0/A1

NOR2XBV4_12TL35 0.000 1.799 0.000 0.018 0.002 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_RC_225_0/ZN

A1 ^ -> ZN ^ NOR2XBV4_12TL35 0.032 1.831 0.000 0.017 0.003 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_RC_253_0/B

AOI21V8_12TR35 0.000 1.831 0.000 0.017 0.003 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_RC_253_0/ZN

B ^ -> ZN v AOI21V8_12TR35 0.015 1.846 0.000 0.012 0.002 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_PHC1794_n_15/I

BUFV5RD_12TR35 0.000 1.847 0.000 0.012 0.002 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_PHC1794_n_15/Z

I v -> Z v BUFV5RD_12TR35 0.023 1.869 0.000 0.008 0.003 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_PHC1345_n_15/I

BUFV8_12TR35 0.000 1.870 0.000 0.008 0.003 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_PHC1345_n_15/Z

I v -> Z v BUFV8_12TR35 0.033 1.902 0.002 0.025 0.020 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_ECOC695_FE_PHN1345_n_15/I

BUFV2_12TL35 0.005 1.908 0.001 0.026 0.020 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_ECOC695_FE_PHN1345_n_15/Z

I v -> Z v BUFV2_12TL35 0.040 1.948 0.000 0.015 0.003 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_ECOC696_FE_PHN1345_n_15/I

BUFV2_12TL35 0.000 1.948 0.000 0.015 0.003 1 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/FE_ECOC696_FE_PHN1345_n_15/Z

I v -> Z v BUFV2_12TL35 0.032 1.980 0.000 0.013 0.002 1.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/wr_l_reg/D

SNDRSNQV4_12TR35 0.000 1.980 0.000 0.013 0.002 1 1.000

————————————————————————————————————————————————————–

Clock Rise Edge 0.000

= Beginpoint Arrival Time 0.000

Other End Path:

————————————————————————————————————————————————————–

Pin Arc Cell Delay Arrival Incr Slew Load Fanout User Generated Clock

Time Delay Derate Adjustment

————————————————————————————————————————————————————–

clk_ctlr_sync clk_ctlr_sync ^ 0.000 0.200 0.003 1

clk_ctlr_sync_I_xIOx/I CLKBUFV8_12TR35 0.000 0.000 0.000 0.200 0.003 1 0.920

clk_ctlr_sync_I_xIOx/Z I ^ -> Z ^ CLKBUFV8_12TR35 0.100 0.100 0.000 0.035 0.019 0.920

clk_ctlr_sync_N_xIOx__L1_I0/I CLKINV12_12TR35 0.004 0.104 0.000 0.035 0.019 1 0.920

clk_ctlr_sync_N_xIOx__L1_I0/ZN I ^ -> ZN v CLKINV12_12TR35 0.030 0.134 0.000 0.033 0.019 0.920

clk_ctlr_sync_N_xIOx__L2_I0/I CLKINV12_12TR35 0.003 0.137 0.000 0.034 0.019 1 0.920

clk_ctlr_sync_N_xIOx__L2_I0/ZN I v -> ZN ^ CLKINV12_12TR35 0.027 0.164 0.000 0.020 0.017 0.920

clk_ctlr_sync_N_xIOx__L3_I0/I CLKINV12_12TR35 0.003 0.167 0.000 0.021 0.017 1 0.920

clk_ctlr_sync_N_xIOx__L3_I0/ZN I ^ -> ZN v CLKINV12_12TR35 0.015 0.182 0.000 0.011 0.005 0.920

clk_ctlr_sync_N_xIOx__I29/I CLKINV16_12TR35 0.000 0.182 0.000 0.011 0.005 1 0.920

clk_ctlr_sync_N_xIOx__I29/ZN I v -> ZN ^ CLKINV16_12TR35 0.010 0.192 0.000 0.006 0.005 0.920

clk_ctlr_sync_N_xIOx__I30/I CLKINV16_12TR35 0.000 0.192 0.000 0.006 0.005 1 0.920

clk_ctlr_sync_N_xIOx__I30/ZN I ^ -> ZN v CLKINV16_12TR35 0.016 0.208 0.000 0.034 0.026 0.920

clk_ctlr_sync_N_xIOx__L4_I0/I CLKINV12_12TR35 0.007 0.215 0.000 0.035 0.026 1 0.920

clk_ctlr_sync_N_xIOx__L4_I0/ZN I v -> ZN ^ CLKINV12_12TR35 0.025 0.240 0.000 0.013 0.008 0.920

databahn_dll_phy/clk_ctlr_sync clk_ctlr_sync ^ databahn_dll_phy 0.240 0.920 clk_ctlr_phase_0 Adj. = 0.000

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I0/I

CLKINV12_12TR35 0.000 0.240 0.000 0.013 0.008 1 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I0/ZN

I ^ -> ZN v CLKINV12_12TR35 0.014 0.254 0.000 0.016 0.009 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I1/I

CLKINV16_12TR35 0.000 0.254 0.000 0.016 0.009 1 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_I1/ZN

I v -> ZN ^ CLKINV16_12TR35 0.012 0.266 0.000 0.007 0.004 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I27/I

CLKINV12_12TR35 0.000 0.266 0.000 0.007 0.004 1 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I27/ZN

I ^ -> ZN v CLKINV12_12TR35 0.009 0.275 0.000 0.009 0.004 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I28/I

CLKINV12_12TR35 0.000 0.275 0.000 0.009 0.004 1 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__I28/ZN

I v -> ZN ^ CLKINV12_12TR35 0.014 0.289 0.000 0.014 0.015 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L1_I0/I

CLKINV16_12TR35 0.001 0.290 0.000 0.014 0.015 2 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L1_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.021 0.310 0.000 0.032 0.025 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L2_I0/I

CLKINV16_12TR35 0.005 0.315 0.000 0.033 0.025 1 0.920

databahn_dll_phy/clk_ctlr_sync_N_xIOx__Fence_N1__L2_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.028 0.343 0.000 0.021 0.026 0.920

databahn_dll_phy/dll_phy_pll_clk_source/deskew_pll/FREF

PLLSM28HKLVDESKEW 0.003 0.346 0.000 0.011 0.026 2 0.920

databahn_dll_phy/dll_phy_pll_clk_source/deskew_pll/FOUTP

FREF ^ -> FOUTP v PLLSM28HKLVDESKEW 0.000 0.972 0.000 0.019 0.025 0.920 clk_phase_0 Adj. = 0.625

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_pll_clkgate/hic_dnt_pll_clkgate/CK

CLKLANQV12_12TR35 0.001 0.973 0.000 0.037 0.025 2 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_pll_clkgate/hic_dnt_pll_clkgate/Q

CK v -> Q v CLKLANQV12_12TR35 0.055 1.028 0.000 0.012 0.004 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand0/A1

CLKNAND2V8_12TR35 0.000 1.028 0.000 0.012 0.004 1 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand0/ZN

A1 v -> ZN ^ CLKNAND2V8_12TR35 0.012 1.041 0.000 0.009 0.004 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand2/A1

CLKNAND2V8_12TR35 0.000 1.041 0.000 0.009 0.004 1 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_clk_bypass_mux/hic_dnt_mux_nand2/ZN

A1 ^ -> ZN v CLKNAND2V8_12TR35 0.012 1.053 0.000 0.013 0.003 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_phybyp_clkgate/hic_dnt_pll_clkgate/CK

CLKLANQV12_12TR35 0.000 1.053 0.000 0.013 0.003 1 0.920

databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_phybyp_clkgate/hic_dnt_pll_clkgate/Q

CK v -> Q v CLKLANQV12_12TR35 0.044 1.097 0.000 0.044 0.025 0.920

databahn_dll_phy/dll_phy_lp_control/inst_hic_lp_clkgate_phy/hic_dnt_io_clkgate/CK

CLKLANQV12_12TR35 0.001 1.098 0.000 0.044 0.025 2 0.920

databahn_dll_phy/dll_phy_lp_control/inst_hic_lp_clkgate_phy/hic_dnt_io_clkgate/Q

CK v -> Q v CLKLANQV12_12TR35 0.056 1.154 0.000 0.033 0.019 0.920

databahn_dll_phy/lp_clk_phy__L1_I0/I

CLKINV16_12TR35 0.002 1.156 0.000 0.033 0.019 2 0.920

databahn_dll_phy/lp_clk_phy__L1_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.026 1.183 0.000 0.024 0.035 0.920

databahn_dll_phy/lp_clk_phy__L2_I0/I

CLKINV16_12TR35 0.012 1.195 0.000 0.034 0.035 1 0.920

databahn_dll_phy/lp_clk_phy__L2_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.032 1.227 0.000 0.040 0.032 0.920

databahn_dll_phy/lp_clk_phy__L3_I0/I

CLKINV16_12TR35 0.010 1.238 0.000 0.044 0.032 1 0.920

databahn_dll_phy/lp_clk_phy__L3_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.033 1.270 0.000 0.027 0.036 0.920

databahn_dll_phy/lp_clk_phy__L4_I0/I

CLKINV16_12TR35 0.012 1.282 0.000 0.035 0.036 1 0.920

databahn_dll_phy/lp_clk_phy__L4_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.033 1.315 0.000 0.044 0.036 0.920

databahn_dll_phy/lp_clk_phy__L5_I0/I

CLKINV16_12TR35 0.013 1.328 0.000 0.051 0.036 1 0.920

databahn_dll_phy/lp_clk_phy__L5_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.036 1.363 0.000 0.027 0.034 0.920

databahn_dll_phy/lp_clk_phy__L6_I0/I

CLKINV16_12TR35 0.011 1.374 0.000 0.034 0.034 1 0.920

databahn_dll_phy/lp_clk_phy__L6_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.033 1.407 0.000 0.045 0.038 0.920

databahn_dll_phy/lp_clk_phy__L7_I0/I

CLKINV16_12TR35 0.013 1.420 0.000 0.052 0.038 1 0.920

databahn_dll_phy/lp_clk_phy__L7_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.035 1.456 0.000 0.024 0.024 0.920

databahn_dll_phy/lp_clk_phy__L8_I0/I

CLKINV16_12TR35 0.005 1.460 0.000 0.025 0.024 1 0.920

databahn_dll_phy/lp_clk_phy__L8_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.025 1.485 0.000 0.033 0.026 0.920

databahn_dll_phy/dll_phy_slice_core/FE_ECOC0_lp_clk_phy/I

CLKINV8_12TR35 0.006 1.491 0.000 0.035 0.026 2 0.920

databahn_dll_phy/dll_phy_slice_core/FE_ECOC0_lp_clk_phy/ZN

I v -> ZN ^ CLKINV8_12TR35 0.023 1.515 0.000 0.011 0.003 0.920

databahn_dll_phy/dll_phy_slice_core/FE_ECOC1_lp_clk_phy/I

CLKINV8_12TR35 0.000 1.515 0.000 0.011 0.003 1 0.920

databahn_dll_phy/dll_phy_slice_core/FE_ECOC1_lp_clk_phy/ZN

I ^ -> ZN v CLKINV8_12TR35 0.013 1.528 0.000 0.015 0.006 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L1_I0/I

CLKINV16_12TR35 0.000 1.528 0.000 0.015 0.006 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L1_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.012 1.540 0.000 0.007 0.004 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L2_I0/I

CLKINV12_12TR35 0.000 1.540 0.000 0.007 0.004 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L2_I0/ZN

I ^ -> ZN v CLKINV12_12TR35 0.008 1.548 0.000 0.008 0.003 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_I_xIOx/I

CLKBUFV8_12TR35 0.000 1.548 0.000 0.008 0.003 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_I_xIOx/Z

I v -> Z v CLKBUFV8_12TR35 0.028 1.576 0.000 0.022 0.008 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/data_slice_data_byte_disable/inst_hic_lp_clkgate_dfi_data_byte_disable_phy/hic_dnt_io_clkgate/CK

CLKLANQV2_12TR35 0.000 1.576 0.000 0.022 0.008 2 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/data_slice_data_byte_disable/inst_hic_lp_clkgate_dfi_data_byte_disable_phy/hic_dnt_io_clkgate/Q

CK v -> Q v CLKLANQV2_12TR35 0.072 1.648 -0.002 0.080 0.009 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L1_I0/I

CLKINV12_12TR35 0.001 1.649 0.001 0.081 0.009 2 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L1_I0/ZN

I v -> ZN ^ CLKINV12_12TR35 0.061 1.710 0.000 0.029 0.017 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L2_I0/I

CLKINV16_12TR35 0.002 1.713 0.000 0.029 0.017 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L2_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.021 1.734 0.000 0.019 0.013 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/hic_dll_xor_clk_wr_dqs/hic_dnt_dll_xor/A1

CLKXOR2V2_12TR35 0.001 1.735 0.000 0.019 0.013 3 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/hic_dll_xor_clk_wr_dqs/hic_dnt_dll_xor/Z

A1 v -> Z v CLKXOR2V2_12TR35 0.053 1.787 0.000 0.034 0.003 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/dll_delay_line_wr_dqs/delay_0/r1/hic_dnt_dll_nand2/A1

CLKNAND2V1_12TR35 0.000 1.787 0.000 0.034 0.003 2 0.920 clk_dqs_0_phase_0 Adj. = 0.000

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/dll_delay_line_wr_dqs/delay_0/r1/hic_dnt_dll_nand2/ZN

A1 v -> ZN ^ CLKNAND2V1_12TR35 0.031 1.818 0.000 0.020 0.001 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/dll_delay_line_wr_dqs/delay_0/r2/hic_dnt_dll_nand2/A2

CLKNAND2V1_12TR35 0.000 1.818 0.000 0.020 0.001 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/dll_delay_line_wr_dqs/delay_0/r2/hic_dnt_dll_nand2/ZN

A2 ^ -> ZN v CLKNAND2V1_12TR35 0.026 1.844 0.000 0.025 0.001 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/hic_dll_qrt_delay_clk_wr_dqs/hic_dnt_dll_qrt_delay/I

ddr101_28nhk_vhsc35

0.000 1.844 0.000 0.025 0.001 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/dll/hic_dll_qrt_delay_clk_wr_dqs/hic_dnt_dll_qrt_delay/Z

I v -> Z v ddr101_28nhk_vhsc35

0.121 1.966 0.000 0.029 0.006 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L1_I0/I

CLKINV16_12TR35 0.000 1.966 0.000 0.029 0.006 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L1_I0/ZN

I v -> ZN ^ CLKINV16_12TR35 0.028 1.994 0.000 0.022 0.030 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L2_I0/I

CLKINV16_12TR35 0.003 1.997 0.000 0.022 0.030 4 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L2_I0/ZN

I ^ -> ZN v CLKINV16_12TR35 0.023 2.020 0.000 0.026 0.020 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L3_I1/I

CLKINV16_12TR35 0.003 2.022 0.000 0.026 0.020 2 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L3_I1/ZN

I v -> ZN ^ CLKINV16_12TR35 0.023 2.045 0.000 0.015 0.017 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L4_I1/I

CLKINV16_12TR35 0.002 2.047 0.000 0.015 0.017 1 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_wrdqs__L4_I1/ZN

I ^ -> ZN v CLKINV16_12TR35 0.020 2.067 -0.003 0.031 0.026 0.920

databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/wr_l_reg/CKN

SNDRSNQV4_12TR35 0.001 2.068 -0.000 0.032 0.026 8 0.920

————————————————————————————————————————————————————–

(1.520 – 0.962) ÷ 1.000 = 0.558 (ns) = 558 (ps)

DDR PHY_TOP STA report:

Path 2: MET Setup Check with Pin databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/wr_l_reg/CKN

Endpoint: databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/wr_l_reg/D (v) checked with trailing edge of 'clk_dqs_0_phase_0'

Beginpoint: databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/write_data_l_reg_reg/Q (v) triggered by leading edge of 'clk_phase_0'

Path Groups: {reg2reg}

Other End Arrival Time 2.068

- Setup 0.075

+ Phase Shift 0.000

+ CPPR Adjustment 0.097

- Uncertainty 0.105

= Required Time 1.985

- Arrival Time 1.980

= Slack Time 0.005

Clock Fall Edge 1.250

= Beginpoint Arrival Time 1.250

-------------------------------------------------------------------------------------------------------------------------------------------------------------- Pin Arc Cell Delay Arrival Incr Slew Load Fanout User Generated Clock Time Delay Derate Adjustment -------------------------------------------------------------------------------------------------------------------------------------------------------------- clk_ctlr_sync clk_ctlr_sync v 1.250 0.200 0.003 1 clk_ctlr_sync_I_xIOx/I CLKBUFV8_12TR35 0.000 1.250 0.000 0.200 0.003 1 1.000 clk_ctlr_sync_I_xIOx/Z I v -> Z v CLKBUFV8_12TR35 0.125 1.375 0.000 0.047 0.019 1.000 clk_ctlr_sync_N_xIOx__L1_I0/I CLKINV12_12TR35 0.004 1.379 0.000 0.047 0.019 1 1.000 clk_ctlr_sync_N_xIOx__L1_I0/ZN I v -> ZN ^ CLKINV12_12TR35 0.037 1.416 0.000 0.024 0.019 1.000 clk_ctlr_sync_N_xIOx__L2_I0/I CLKINV12_12TR35 0.004 1.420 0.000 0.025 0.019 1 1.000 clk_ctlr_sync_N_xIOx__L2_I0/ZN I ^ -> ZN v CLKINV12_12TR35 0.027 1.447 0.000 0.029 0.017 1.000 clk_ctlr_sync_N_xIOx__L3_I0/I CLKINV12_12TR35 0.003 1.450 0.000 0.030 0.017 1 1.000 clk_ctlr_sync_N_xIOx__L3_I0/ZN I v -> ZN ^ CLKINV12_12TR35 0.021 1.471 0.000 0.010 0.005 1.000 ... databahn_dll_phy/clk_ctlr_sync clk_ctlr_sync v databahn_dll_phy 1.525 1.000 clk_ctlr_phase_0 Adj. = 0.000 ... databahn_dll_phy/dll_phy_pll_clk_source/deskew_pll/FREF PLLSM28HKLVDESKEW 0.004 1.641 0.000 0.016 0.026 2 1.000 databahn_dll_phy/dll_phy_pll_clk_source/deskew_pll/FOUTP FREF v -> FOUTP ^ PLLSM28HKLVDESKEW 0.000 0.391 0.000 0.017 0.026 1.000 clk_phase_0 Adj. = -1.250 databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_pll_clkgate/hic_dnt_pll_clkgate/CK CLKLANQV12_12TR35 0.001 0.392 0.000 0.034 0.026 2 1.000 databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_pll_clkgate/hic_dnt_pll_clkgate/Q CK ^ -> Q ^ CLKLANQV12_12TR35 0.052 0.445 0.000 0.012 0.004 1.000 ... databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_phybyp_clkgate/hic_dnt_pll_clkgate/CK CLKLANQV12_12TR35 0.000 0.474 0.000 0.009 0.004 1 1.000 databahn_dll_phy/dll_phy_pll_clk_source/inst_hic_phybyp_clkgate/hic_dnt_pll_clkgate/Q CK ^ -> Q ^ CLKLANQV12_12TR35 0.042 0.516 0.000 0.031 0.026 1.000 databahn_dll_phy/dll_phy_lp_control/inst_hic_lp_clkgate_phy/hic_dnt_io_clkgate/CK CLKLANQV12_12TR35 0.001 0.517 0.000 0.031 0.026 2 1.000 databahn_dll_phy/dll_phy_lp_control/inst_hic_lp_clkgate_phy/hic_dnt_io_clkgate/Q CK ^ -> Q ^ CLKLANQV12_12TR35 0.048 0.565 0.000 0.025 0.019 1.000 ... databahn_dll_phy/dll_phy_slice_core/FE_ECOC1_lp_clk_phy/I CLKINV8_12TR35 0.000 0.948 0.000 0.012 0.003 1 1.000 databahn_dll_phy/dll_phy_slice_core/FE_ECOC1_lp_clk_phy/ZN I v -> ZN ^ CLKINV8_12TR35 0.014 0.962 0.000 0.010 0.006 1.000 databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L1_I0/I CLKINV16_12TR35 0.000 0.963 0.000 0.010 0.006 1 1.000 databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy__L1_I0/ZN I ^ -> ZN v CLKINV16_12TR35 0.011 0.973 0.000 0.008 0.004 1.000 ... databahn_dll_phy/dll_phy_slice_core/data_slice_0/data_slice_data_byte_disable/inst_hic_lp_clkgate_dfi_data_byte_disable_phy/hic_dnt_io_clkgate/CK CLKLANQV2_12TR35 0.001 1.014 0.000 0.017 0.009 2 1.000 databahn_dll_phy/dll_phy_slice_core/data_slice_0/data_slice_data_byte_disable/inst_hic_lp_clkgate_dfi_data_byte_disable_phy/hic_dnt_io_clkgate/Q CK ^ -> Q ^ CLKLANQV2_12TR35 0.072 1.087 0.002 0.063 0.009 1.000 ... databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L16_I20/I CLKINV16_12TR35 0.001 1.481 0.000 0.039 0.027 4 1.000 databahn_dll_phy/dll_phy_slice_core/data_slice_0/clk_phy_dfi_data_byte_en__L16_I20/ZN I v -> ZN ^ CLKINV16_12TR35 0.039 1.520 0.000 0.022 0.027 1.000 databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/write_data_l_reg_reg/CK SDRNQV2_12TR35 0.002 1.521 0.000 0.022 0.027 18 1.000 databahn_dll_phy/dll_phy_slice_core/data_slice_0/io_datacell_3/write_data_l_reg_reg/Q CK ^ -> Q v SDRNQV2_12TR35 0.137 1.658 0.000 0.014 0.001 1.000 ...

CCOpt

CCOpt extends CCOpt-CTS to replace traditional global skew balancing with a combination of CTS, timing driven useful skew, and datapath optimization.

In traditional CTS flows an ideal clock model is used before CTS to simplify clock timing analysis. With the ideal clock model, launch and capture clock paths are assumed to have the same delay. After CTS, the ideal clock model is replaced by a propagated clock model that takes account of actual delays along clock launch and capture paths.

In traditional CTS global skew balancing attempts to make the propagated clock timing match the ideal mode clock timing by balancing the insertion delay (clock latency) between all sinks. However, a number of factors combine such that skew balancing does not lead to timing closure. These include:

- OCV – On-chip variation means that skew, measured using a single metric such as the ‘late’ configuration of a delay corner, no longer directly corresponds to timing impact because launch and capture paths have differing timing derates. In addition, Common Path Pessimism Removal (CPPR) and per-library cell timing derates mean that it is not possible to accurately estimate clock or datapath timing without synthesizing a clock tree. Advanced OCV (AOCV) further complicates this by adding path and bounding box dependent factors.

- Clock gating – Clock gating uses datapath signals to inhibit or permit clock edges to propagate from a clock source to clock sinks. The clock arrival time at a clock gating cell is unknown prior to CTS and this arrival time determines the required time for the datapath control signal to reach the clock gating cell enable input. Therefore the setup slack at a clock gating enable input is hard to predict preCTS. In addition, clock gating cells have an earlier clock arrival time than regular sinks and are therefore often timing critical. Typically, the fan-in registers controlling clock gating may need to have an earlier clock arrival time than regular sinks in order to avoid a clock gating slack violation – which means the fan-in registers need to be skewed early.

- Unequal datapath delays – Front end logic synthesis will attempt to ensure logic between registers is roughly delay balanced to optimize the target clock frequency. However, with wire delay dominating many datapath stages it is likely that after placement and preCTS optimization there will exist some combinational paths with unavoidably longer delays than others. Useful skew clock scheduling permits slack to be moved between register stages to increase clock frequency. In contrast, global skew balancing is independent of timing slack. In addition, CCOpt useful skew scheduling can avoid unnecessarily balancing of sinks where there is excess slack in order to reduce clock area and clock power.

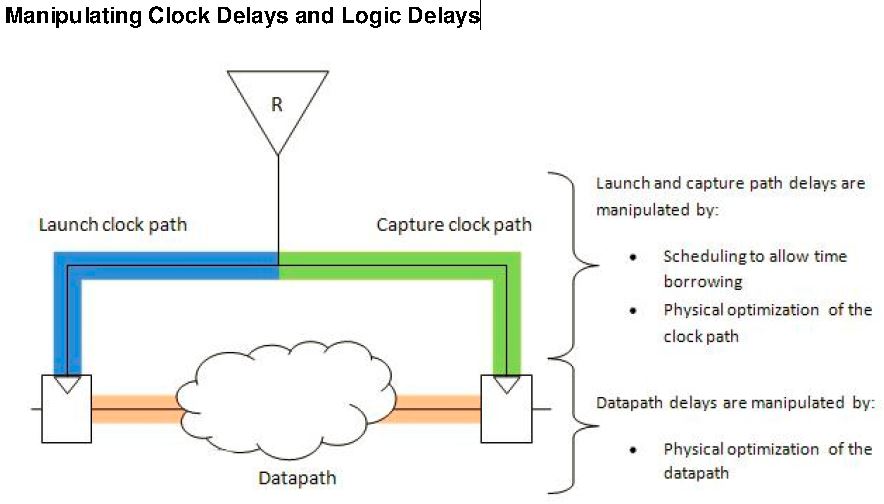

CCOpt treats both clock launch, clock capture, and datapath delays as flexible parameters that can be manipulated to optimize timing as illustrated below.

Manipulating Clock Delays and Logic Delays

At each clock sink (flip-flop) in the design, CCOpt can adjust both datapath and clock delays in order to improve negative setup timing slack – specifically the high effort path group(s) WNS. This is performed using the propagated clock timing model at all times.

Comments

So empty here ... leave a comment!