Timing verification

Two primary checks are setup and hold checks. Once a clock is defined at clock pin of a flip-flop (FF), setup and hold checks are automatically inferred for the FF.

Timing checks are generally performed at multiple conditions including worst-case slow condition and best-case fast condition. Typically, worst-case slow condition is critical for setup check and best-case fast condition is critical for hold check – though hold check may be performed at worst-case slow condition also.

1. Setup timing check

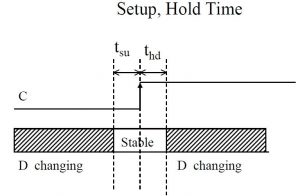

A setup timing check verifies timing relationship between clock and data pin of a FF so that setup requirement is met. In other words, setup check ensures that data is available at input of FF before it is clocked in FF. The data should be stable for a certain amount of time, namely setup time of FF, before active edge of clock arrives at the FF.

Setup requirement ensures that data is captured reliably into FF.

Figure 1 Setup requirement of a FF

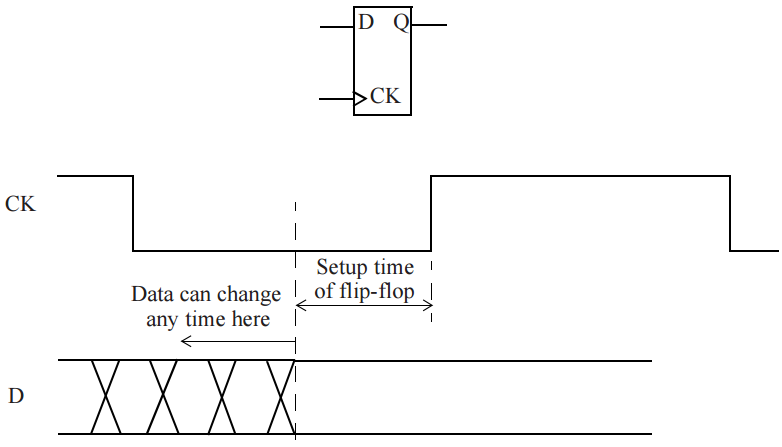

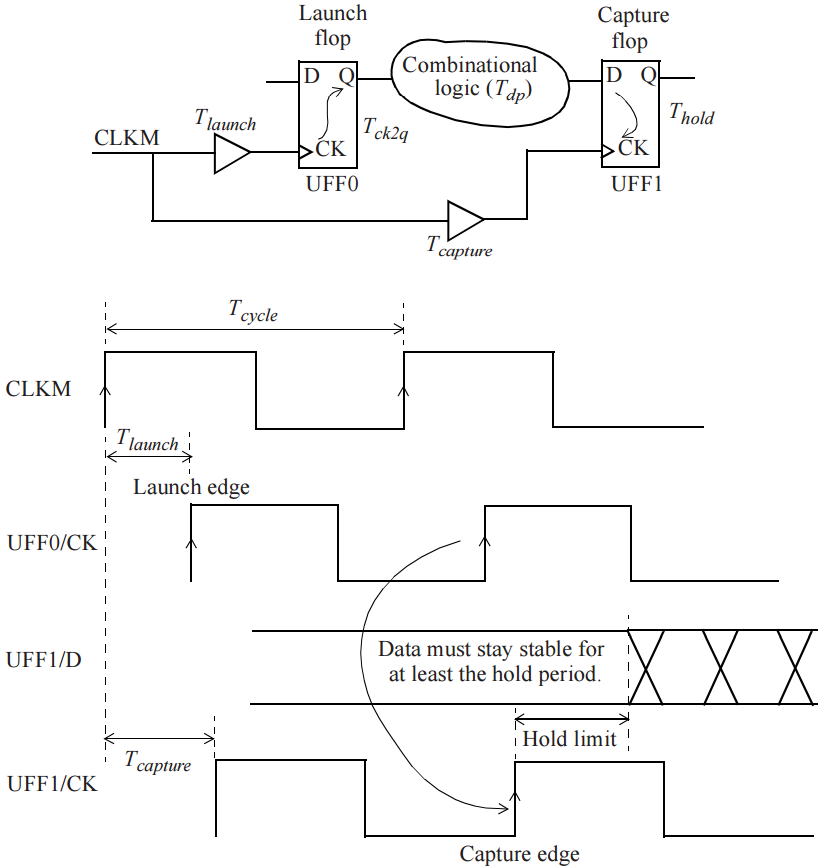

In general, there is a launch FF – which launches data and a capture FF which captures data whose setup time must be satisfied. The setup check validates the long (or max) path from launch FF to capture FF. The clocks to two FF can be the same or can be different.

Figure 2 Data and clock signals for setup check

Tlaunch + Tck2q + Tdp < Tcapture + Tcycle - Tsetup

Setup check impose max constraint for paths to data pin on the capture FF; the slowest path to D pin of capture FF needs to be determined. This implies that setup check is verified using the slowest paths. Thus, setup check is typically performed at slow timing corner.

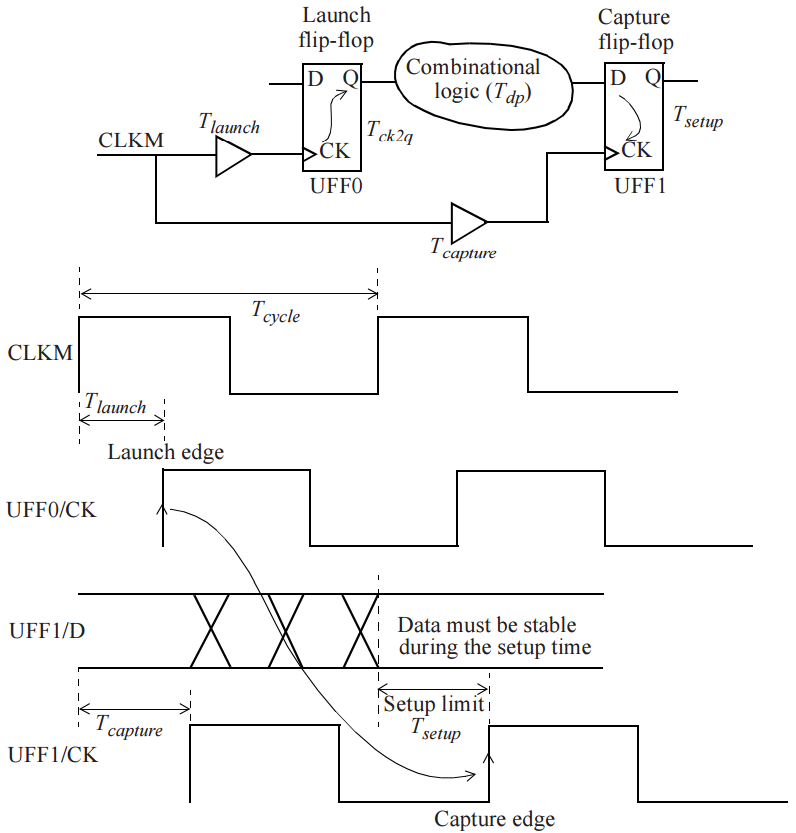

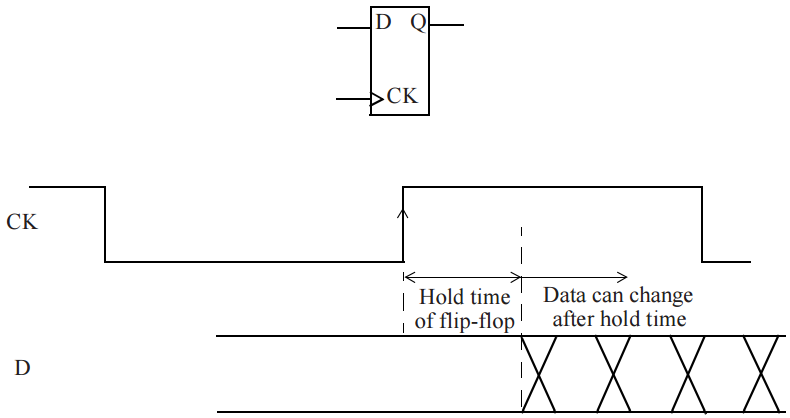

2. Hold timing check

Hold timing check ensures that a FF output value that is changing does not pass through to a capture FF and overwrite its output before FF has a chance to capture its original value. Hold specification of a FF requires that data being latched should be held stable for a specified amount of time after active edge of clock.

Figure 3 Hold requirement of a FF

Figure 4 Data and clock signals for hold check

Tlaunch + Tck2q + Tdp > Tcapture + Thold

Hold check impose min constraint for paths to data pin on the capture FF; the fastest path to D pin of capture FF needs to be determined. This implies that hold check is verified using the fastest paths. Thus, hold check is typically performed at fast timing corner.

Comments

So empty here ... leave a comment!