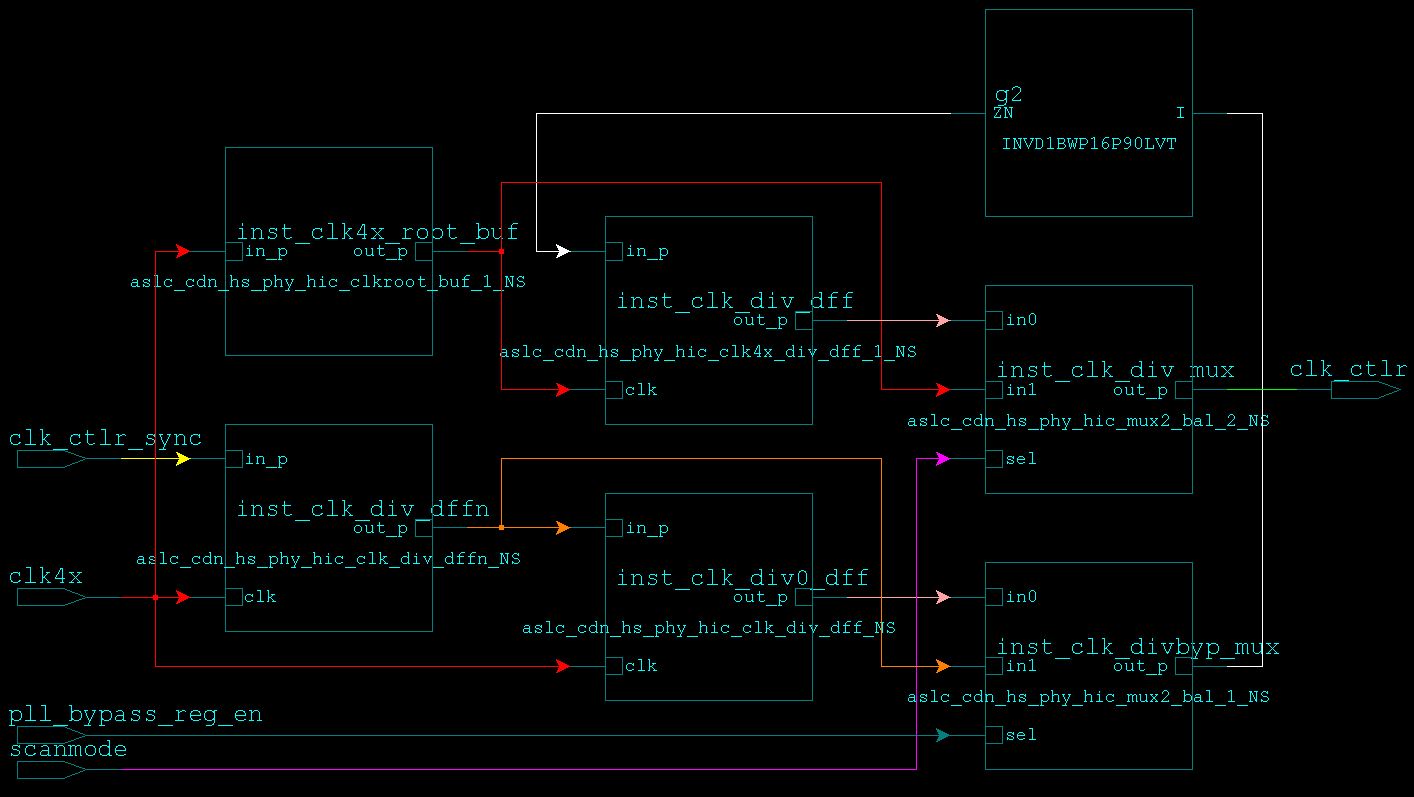

Clock divider and CTS

Turbodebug check Design netlist about clk div timing path:

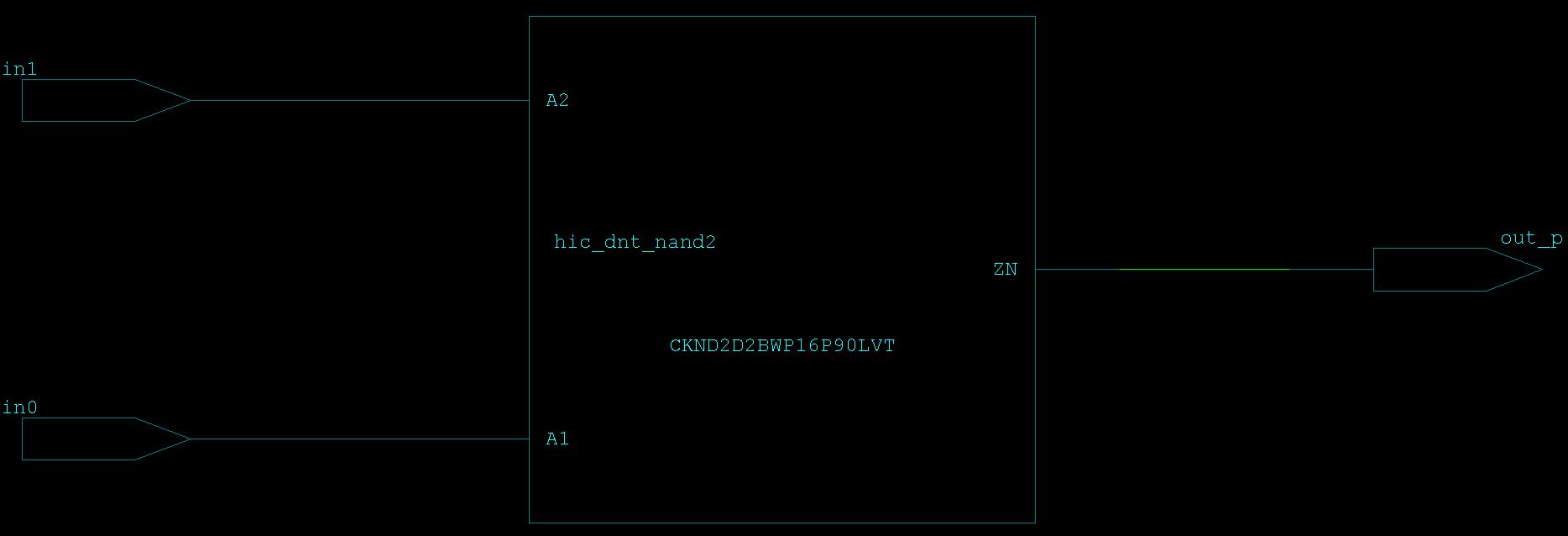

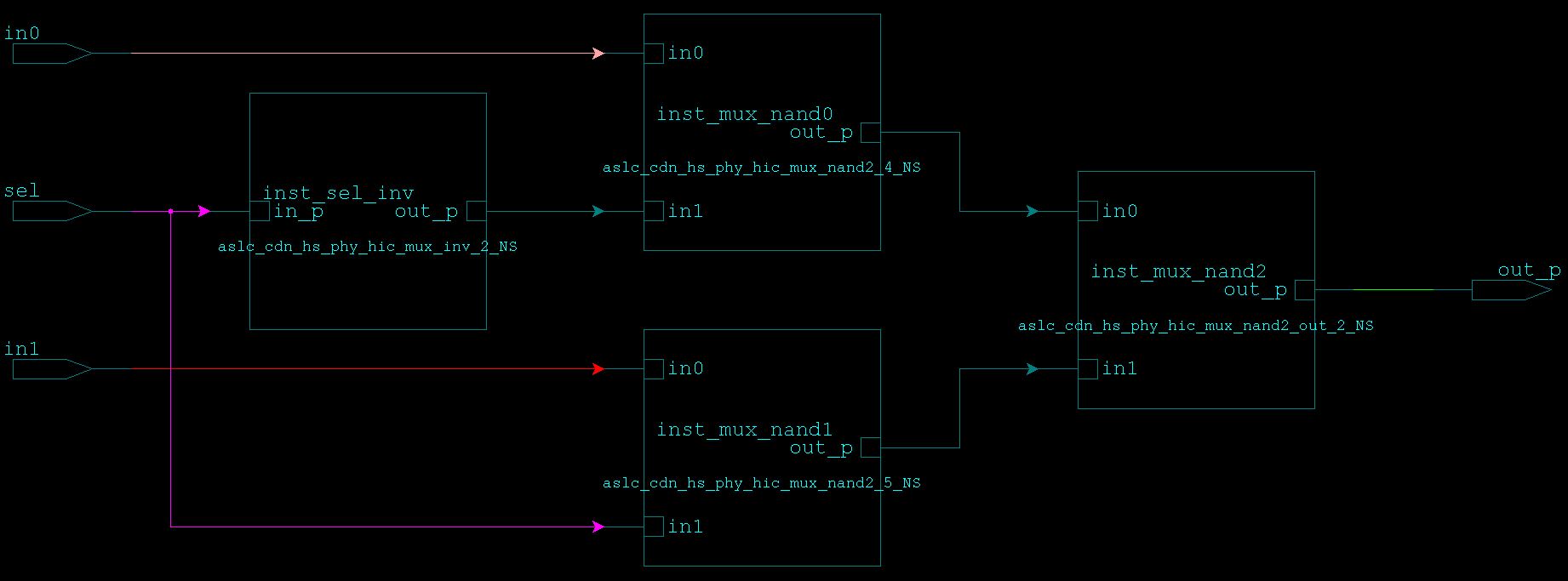

Fig. 2, 3 Design/inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN

Fig. 2, 3 Design/inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN

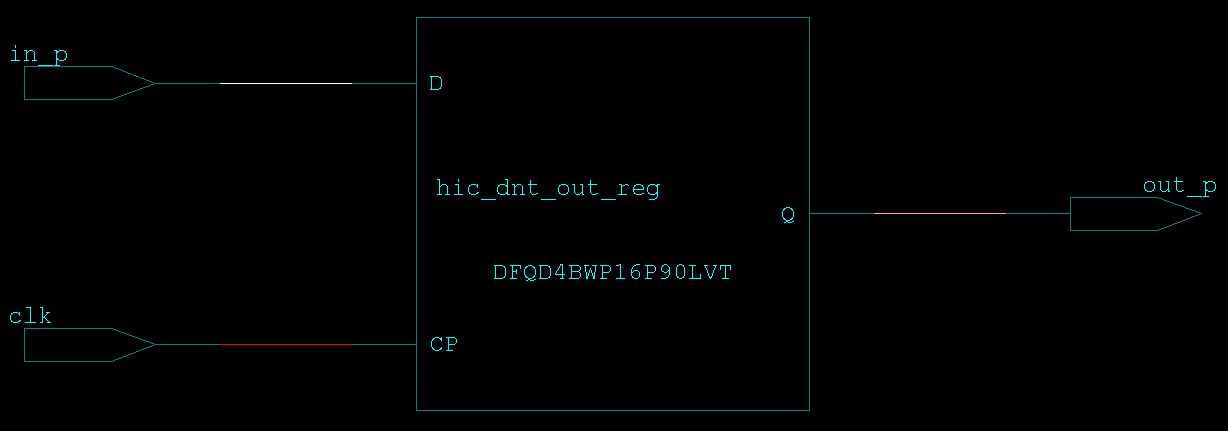

Fig. 4 Design/inst_clk_div/inst_clk_div_dff/hic_dnt_out_reg/Q (constraint below create_generated_clock set it as RootPin, but design inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN as RootPin in CTS Spec file, as Fig. 4 Q pin (out_p) connects to Fig. 2 in0 actually)

Fig. 4 Design/inst_clk_div/inst_clk_div_dff/hic_dnt_out_reg/Q (constraint below create_generated_clock set it as RootPin, but design inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN as RootPin in CTS Spec file, as Fig. 4 Q pin (out_p) connects to Fig. 2 in0 actually)

#Constraint

create_clock [get_ports clk4x ] -name dummy_clk4x -period 0.5*0.833 -waveform "0 0.25*0.833"

create_generated_clock -name slice_clk_ctlr_phase_0 -edges {1 5 9} -add \

-source [get_ports clk4x] \

-master [get_clock dummy_clk4x] \

[get_pin inst_clk_div/inst_clk_div_dff/hic_dnt_out_reg/Q]

#CTS Spec file

ClkGroup + inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN

GlobalLeafPin + inst_clk_div/inst_clk_div_mux/inst_mux_nand0/hic_dnt_nand2/A1 + inst_clk_div/inst_clk_div_mux/inst_mux_nand1/hic_dnt_nand2/A1

GlobalUnsyncPin + inst_clk_div/inst_clk_div_dffn/hic_dnt_out_reg/CPN + inst_clk_div/inst_clk_div0_dff/hic_dnt_out_reg/CP + inst_clk_div/inst_clk_div_dff/hic_dnt_out_reg/CP

AutoCTSRootPin clk4x

AutoCTSRootPin inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN

#As Fig. 4 Q pin (out_p) connects to Fig. 2 in0 actually, design inst_clk_div/inst_clk_div_mux/inst_mux_nand2/hic_dnt_nand2/ZN as RootPin, it is more clear to CTS.

Comments

So empty here ... leave a comment!