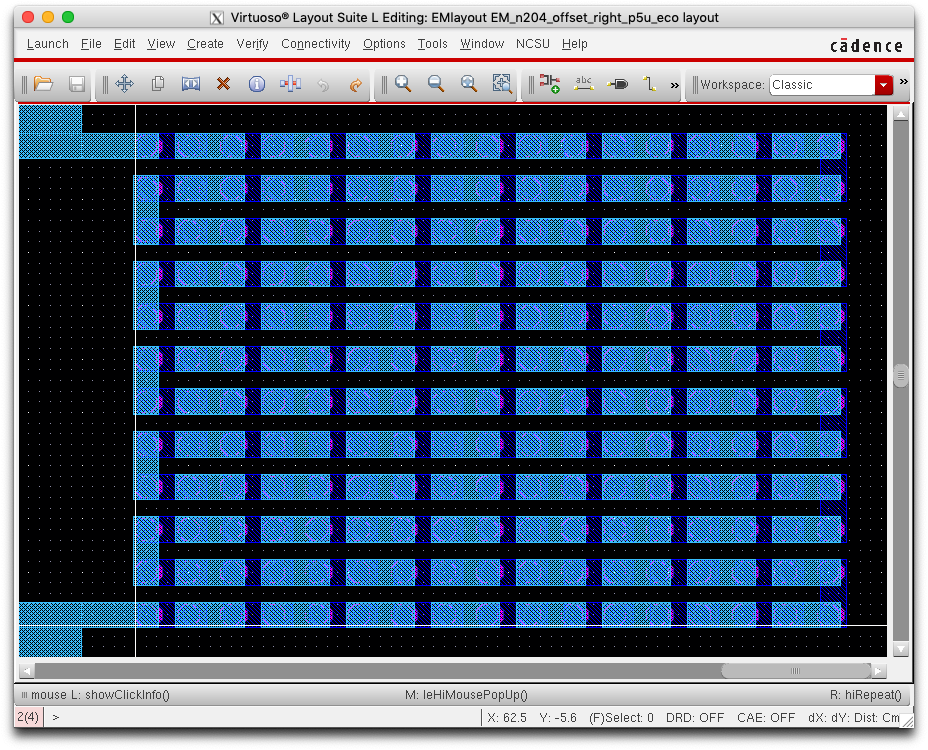

Cadence Virtuoso

I used Cadence® Virtuoso® to design layout for Electromigration (EM) Test Pad for tape-out with Harris Corporation and ICAMR in Fall 2016, partner was Novati Technologies, Inc. who I submitted GDSII to. Map file was from MOSIS: https://www.eda.ncsu.edu/wiki/MOSIS_Layers. The test pad size: 120um x 120 um. Pitch: 250um, which means 130um spacing between 2 test… read more »